# 고효율 버스트 모드 제어를 이용한 파워 설계 방안

# 주성용 삼성전자 VD 사업부

# Power Design Method Using High Efficiency Burst Mode Control

Sung-Yong Joo Samsung Electronics Visual Display Business

### **ABSTRACT**

본 논문에서는 컨버터의 Burst Mode제어 방법에 대해고려해야 할 부분과 실제 발생하는 문제점을 해결 할 수 있는 방법에 대해 새로운 접근방식을 소개한다. [1][2][3]

소음 및 효율개선 그리고 PFC Burst 제어를 통해 발생 할 수 있는 제품구조에서 문제점을 해결 할 수 있는 방법을 소개한다. 제안하는 방식은 입력 전압에 따른 Burst 동작시 피크 전류를 제한하고 소음 문제 및 대기전력을 개선 할 수 있는 방법 및이에 따른 이론적 타당성을 검증한다.

### 1. 서 론

TV SET의 두께가 얇아질수록 회로물에 사용되는 부품의 Depth는 낮아지게 되고 Depth를 만족시키기 위해 PCB에 Hole을 내어 부품을 배치시키는 파워가 요구된다. 그리고 이런 구조에서 기구 chassis 금속물과 부품간 거리가 가까워 자기적 간섭이 발생하며 부품 발열 및 소음등의 문제를 유발시킨다.

그림 1. PCB Hole 및 부품 실장

제품은 Power Off 이후 소비 전력 사양을 만족하기 위해서 절전모드로 동작한다. [4] [5] [6] 이때 SMPS는 전력 소모를 최소화하기 위해서 Burst Mode로 동작하기 때문에 AC 입력 전류의 Peak성 전류가 AC Noise Filter와 Film Cap 부품에 유입된다. 이 상황에서의 전류 형태는 Line Filter의 자성체(Core)와 Chassis의 금속간 자기장이 형성되어 Core 떨림을 발생하는 원인이 되기도 한다. 그리고 이를 개선하기 위해 Line Filter에 차폐용 Core를 적용하여 소음 문제를 개선하는 것은 해당부품의 재료비 상승, 작업성 저하의 문제점이 있다.

그림2는 이에 대한 개선을 위해 추가된 차폐 시트의 구조이며 가청 소음 구간의 Flux움직임이 Chassis미치는 영향에 대한 개선이 가능한 형상이다.

그림 2. Flux 영향 개선을 위한 자폐 Core 내장 Filter

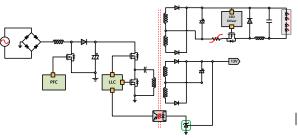

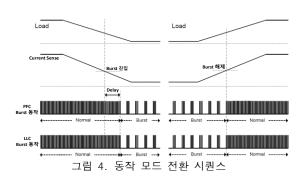

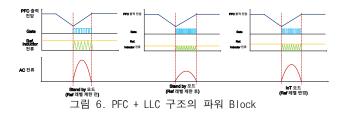

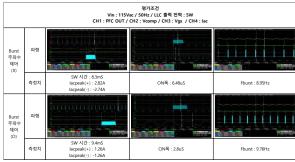

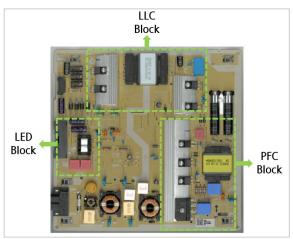

그림 3. PFC + LLC 구조의 파워 Block

그림3은 PFC+LLC 파워 구조에서 Burst Mode 진입과 해제 구간에 대한 시퀀스를 나타내고 있으며 출력 전력이 서서히 감소하는 전류를 감지해서 Burst Mode의 동작모드를 구분해서 자동으로 전환이 가능하게 동작한다. 해당 Burst동작시 발생하는 Peak전류를 제한하는 상황이 필요한가전기기에서의 PFC Burst 구동 방법에 대해 논의를 하려고한다. 동작 모드는 기본적으로 LLC 전류를 센싱하는 기능에서 결정이 되지만 부하가 급변하는 구간에서는 출력전압이일시적으로 떨어지는 문제가 발생 할 수 있으니 이 부분에 대한 응답특성을 고려한 설계가 필요하다. [7][8][9]

#### 2. 제안하는 컨버터의 동작 원리

제안하는 회로는 PFC회로의 Burst 동작 시 발생하는 Peak전류를 제한하는 동작에 연관된 부분이며 이는 실제 발생하는 대기모드 소음 개선에 필요한 부분이라 할 수 있다. 특히 AC전압이 낮으면 고전압으로 변환하기 위한 On Time이 길어지게 되며 인덕터에 흐르는 전류는 증가하게된다. 실제 발생하는 소음 문제는 AC 저전압에서 더 크게 발생하게 되는 상황이며 제안하는 LLC 컨버터는 AC 저전압고전압에서의 동작을 구분하여 대기전력 상승없이 최적의Burst 동작을 구현하는 것에 회로의 목적이 있다.

## 3. 제안하는 컨버터의 분석

#### 3.1 제안하는 컨버터의 Burst 동작 제어 방법

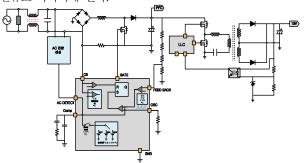

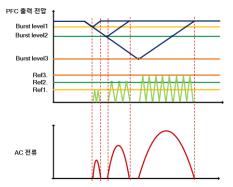

일반 동작 상태에서는 Burst동작을 하지 않으며 세트 대기전력을 만족시키기 위한 대기 모드 동작은 및 Current Sensing 블록에서 특정 이하의 부하가 유지되면 Burst 동작을 시작한다. Burst Mode로 동작하면 센싱블럭의 레벨에 따라 Burst Ref 전압이 결정된다. 설정된 Ref1,Ref2,Ref3의 전압에 따라 PFC Peak 전류가 제한되면 AC라인에 흐르는 전류도 작아지게 된다.

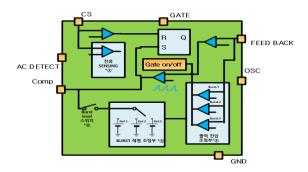

그림 5. Burst 동작 제어 구성

그림5는 전체 PFC Burst를 제어하는 전체 구성도를 나타내며 기준 전압이 너무 낮으며 전류 Peak는 작게 유지 되지만 주파수가 빨라져 가청주파수로 동작하는 문제가 발생하기도 한다. 이것을 제어 하기 위해서 Sensing 블록에서 전류를 센싱하고 전압레벨을 조정하여 Peak전류를 여러 단계로 제한하기도 한다.

최근 SET 대기모드에서도 Network와 연결된 IoT 모드가 동작 하기 때문에 SMPS 부하가 증가하는 구간이 발생한다. Ref전압 변경을 통해 입력 전류를 조정할 수 있으며 출력 전압과 연계하면 좀더 다양한 제어가 가능하다. 그림7은 입력과 출력 2가지 정보를 모두 이용해서 제어했을 경우의 블록도를 나타낸다.

그림 7. Ref 및 PFC출력 전압으로 Peak전류 제한

출력 전압조정부는 PFC출력 전압을 단계별로 센싱하며 Burst 레벨 제어부와 연계하여 Gate Signal을 On/Off하여 출력 전압의 폭을 제어 할 수 있다. 또한 고주파 버스트 제어를 이용하면 경부하 효율을 개선 할 수 있는 방법도 적용이 가능하다.

# 3.2 주파수 구간에 다른 효율개선

3개의 구간으로 설정이 가능하며 기존 동작에서 가청 주파수를 벗어나면서 효율 개선이 가능한 장점이 있다. 효율 개선에대한 내용은 아래 그림8에서 확인 할 수 있으며 Burst의주기를 나눠서 부하별로 효율 개선이 가능한 부분을 확인 할수 있다.

그림 8. Burst 주파수제어를 이용한 경부하 효율개선

### 3. 제안하는 컨버터의 실험 결과

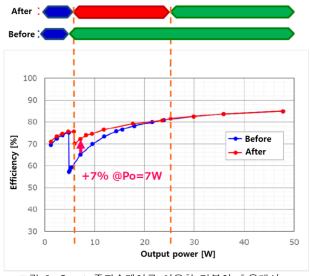

제안하는 컨버터를 구성하는 실험은 55" LED에 들어가는 파워기준으로 개선된 부분을 검토 하였으며 관련 시험결과는 아래와 같이 확인 가능하다. Burst동작에 개선 부분에 대한 입력전류 Peak는 2.8A → 1.2A 수준으로 55% 저감된부분을 확인 할 수 있었으며 이 효과는 소음 및 경부하 효율개선된 내용으로 확인이 가능하다.

그림 9. Burst 주파수제어를 이용한 경부하 효율개선

그림 10. 55" TV 고효율 파워 Board

#### 4. 결 론

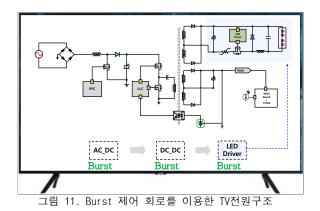

본 논문에서는 LED 구동을 목적으로 구성된 PFC, LLC 동작에 있어서 Burst모드를 기반으로 하는 고효율 스위칭 방법에 대해 제안하였다. TV를 시청하는 시간 뿐만 아니라 대기모드에서의 감성 소음을 회로적으로 개선 하는 방법을 제시하였으며 이는 슬림화되는 전자기기 그리고 효율을 우선으로 개선되어야 하는 파워구조에서 경부하 이하의 영역에서 좀 더 구체적인 제어 회로 방식을 통해 Burst모드의 새로운 접근방식을 제시하였다. AC/DC, DC/DC 그리고 LED Dimming회로를 이용한 광원제어 까지 효율을 개선하고자 하는 시도는 앞으로 많은 부분이 시도될 예정이다. 파워 응용 회로와 적용되는 부품의 발전이 조화롭게 이루어 진다면 여러가지 Display기기에 확장 적용이 가능하다고 판단되며 가격경쟁력에 있어서도 간소화되는 파워 블럭을 이용한다면 많은 효과를 기대 하 수 있을 것이다. 제안된 IDEA 및 실험결과를 보드실장 평가로 확인이 가능하였으며 추가적인 경부하 효율 개선에 있어서도 여러가지 방법으로 접근이 가능함을 증명하였다.

## 참 고 문 헌

- [1] W. Feng, F. C. Lee and P. Mattavelli, "Optimal Trajectory Control of Burst Mode for LLC Resonant Converter," in IEEE Transactions on Power Electronics, vol. 28, no. 1, pp.457–466, Jan. 2013, doi: 10.1109/TPEL.2012.2200110.

- [2] B. Wang X. Xin S. Wu H. Wu and J. Ying "Analysis and implementation of LLC burst mode for light load efficiency improvement" Proc. 24th Annu IEEE Appl. Power Electron. Conf. Expo. pp. 58-64 Feb. 2009.

- [3]Y.Jang and M. M. Jovanovic "Light-load efficiency optimization method" IEEE Trans. Power Electron. vol. 25 no. 1 pp. 67-74 Jan. 2010.

- [4] R. Oruganti and F. C. Lee "Resonant power processors— Part I: State plane analysis" IEEE Trans. Ind. Appl. vol. IA-21 no. 6 pp. 1453-1460 Nov. 1985.

- [5] R. Oruganti and F. C. Lee "Resonant power processors— Part I: State plane analysis" IEEE Trans. Ind. Appl. vol. IA-21 no. 6 pp. 1453-1460 Nov. 1985.

- [6] G. -C. Huang, T. -J. Liang and Kai-Hui Chen, "Losses analysis and low standby losses quasi-resonant flyback converter design," 2012 IEEE International Symposium on Circuits and Systems (ISCAS), Seoul, Korea (South), 2012, pp. 217-220, doi: 10.1109/ISCAS.2012.6271718.

- [7] I. Wacyk, D. Giannopoulos and S. Mukherjee, "Plugging the global power leak [appliance standby mode power reduction]," in IEE Review, vol. 46, no. 6, pp. 23–27, Nov. 2000, doi: 10.1049/ir:20000608.

- [8] C. -Y. Huang, T. -J. Liang, K. -H. Chen and C. -Y. Li, "Primary-side feedback control IC design for flyback converter with energy saving burst mode," 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 2018, pp. 2054-2061, doi: 10.1109/APEC.2018.8341300.

- [9] E. -S. Kim, B. -G. Chung, S. -H. Jang, M. -G. Choi and M. -H. Kye, "A study of novel flyback converter with very low power consumption at the standby operating mode," 2010 Twenty-Fifth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Palm Springs, CA, USA, 2010, pp. 1833-1837, doi: 10.1109/APEC.2010.5433482